(简答题)

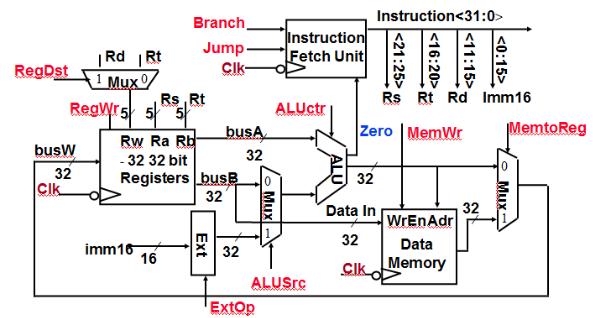

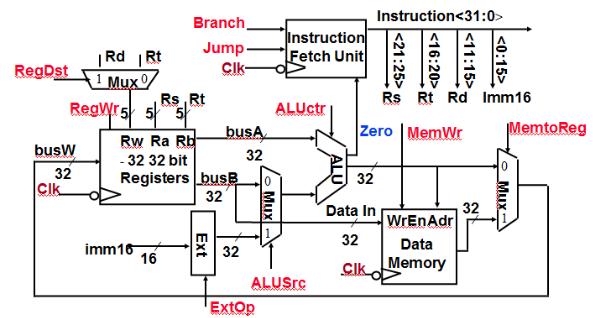

假定下图单周期数据通路对应的控制逻辑发生错误,使得在任何情况下控制信号RegWr、RegDst、Branch、MemWr、ExtOp、R-type总是为0,则哪些指令不能正确执行?为什么?

正确答案

答案解析

略

相似试题

(简答题)

假定有一条MIPS伪指令“Bcmp $t1,$t2,$t3”,其功能是实现对两个主存块数据的比较,$t1和$t2中分别存放两个主存块的首地址,$t3中存放数据块的长度,每个数据占四个字节,若所有数据都相等,则将0置入$t1;否则,将第一次出现不相等时的地址分别置入$t1和$t2并结束比较。若$t4和$t5是两个空闲寄存器,请给出实现该伪指令的指令序列,并说明在类似于P.185图6.32的多周期数据通路中执行该伪指令时要用多少时钟周期。

(填空题)

为了进行数据传输,在数据传输之前先要在发送站与接收站之间建立一条逻辑通路,这种交换方式称为()。

(填空题)

在DLX指令实现的简单数据通路中,()和()指令需要4个时钟周期,其它指令需要5个时钟周期。

(填空题)

在DLX指令实现的简单数据通路中,IF是指取指令周期,ID指()、EX指()、WB指写回周期。

(填空题)

在DLX指令实现的简单数据通路中,在WB周期中,有两大类指令执行操作()和()指令。

(填空题)

在DLX指令实现的简单数据通路中,在ID周期中,指令的()操作和()操作是并行进行的。

(简答题)

减少流水线处理分支指令时的暂停时钟周期数的技术途径是什么?其流水线数据通路应如何改进?

(简答题)

假设数据通路中各主要功能单元的操作时间为:存储单元:200ps;ALU和加法器:100ps;寄存器堆读口或写口:50ps。程序中指令的组成比例为:取数25%、存数10%、ALU52%、分支11%、跳转2%。假设时钟周期取存储器存取时间的一半,MUX、控制单元、PC、扩展器和传输线路等的延迟都忽略不计,则下面的实现方式中,哪个更快?快多少? (1)单周期方式:每条指令在一个固定长度的时钟周期内完成; (2)多周期方式:每类指令时钟数:取数-7,存数-6,ALU-5,分支-4,跳转-4; (3)流水线方式:取指1、取指2、取数/译码、执行、存取1、存取2、写回7段流水线;没有结构冒险;数据冒险采用“转发”技术处理;load指令与后续各指令之间存在依赖关系的概率分别1/2、1/4、1/8、…;分支延迟损失时间片为2,预测准确率为75%;不考虑异常、中断和访问失效引起的流水线冒险。

(简答题)

假定某计算机的总线采用奇校验,每8位数据有一位校验位,若在32位数据线上传输的信息是8F 3C AB 96H,则对应的4个校验位应为什么?若接受方收到的数据信息和校验位分别为87 3C AB 96H和0101B,则说明发生了什么情况,并给出验证过程。