(简答题)

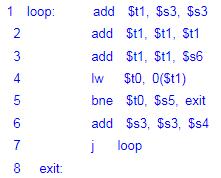

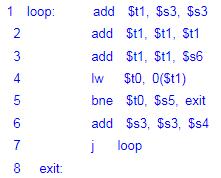

在一个采用“取指、译码/取数、执行、访存、写回”的五段流水线中,若检测结果是否为“零”的操作在执行阶段进行,则分支延迟损失时间片(即分支延迟槽)为多少?以下一段MIPS指令序列中,在考虑数据转发的情况下,哪些指令执行时会发生流水线阻塞?各需要阻塞几个时钟周期?

正确答案

答案解析

略

相似试题

(简答题)

以下指令序列中,哪些指令对发生数据相关?假定采用“取指、译码/取数、执行、访存、写回”五段流水线方式,那么不用“转发”技术的话,需要在发生数据相关的指令前加入几条nop指令才能使这段程序避免数据冒险?如果采用“转发”是否可以完全解决数据冒险?不行的话,需要在发生数据相关的指令前加入几条nop指令才能使这段程序不发生数据冒险?

(简答题)

假设数据通路中各主要功能单元的操作时间为:存储单元:200ps;ALU和加法器:100ps;寄存器堆读口或写口:50ps。程序中指令的组成比例为:取数25%、存数10%、ALU52%、分支11%、跳转2%。假设时钟周期取存储器存取时间的一半,MUX、控制单元、PC、扩展器和传输线路等的延迟都忽略不计,则下面的实现方式中,哪个更快?快多少? (1)单周期方式:每条指令在一个固定长度的时钟周期内完成; (2)多周期方式:每类指令时钟数:取数-7,存数-6,ALU-5,分支-4,跳转-4; (3)流水线方式:取指1、取指2、取数/译码、执行、存取1、存取2、写回7段流水线;没有结构冒险;数据冒险采用“转发”技术处理;load指令与后续各指令之间存在依赖关系的概率分别1/2、1/4、1/8、…;分支延迟损失时间片为2,预测准确率为75%;不考虑异常、中断和访问失效引起的流水线冒险。

(简答题)

处理器的“取指-译码-执行周期”是指什么?

(填空题)

按照I/O地址译码电路采用的元器件来分,可分为()译码、()译码和()译码;按译码电路的形式来看,又可分为()译码和()译码。

(单选题)

在8086/8088CPU中,为了减少CPU等待取指所需的时间,设置了()

(简答题)

在采用地址流水线方式时,地址锁存在什么时间进行?地址译码器位于地址锁存器之前有什么好处?这样做有什么要求?

(单选题)

若存储体中有1K个存储单元,采用双译码方式时要求译码输出线为()

(简答题)

在8088CPU中,为了减少CPU的等待取指所需的时间,设置了什么?

(简答题)

在8086最小方式系统总线上扩充设计16K字节的SRAM存储器电路,SRAM芯片选用Intel6264,起始地址从04000H开始,译码器电路采用74LS138。